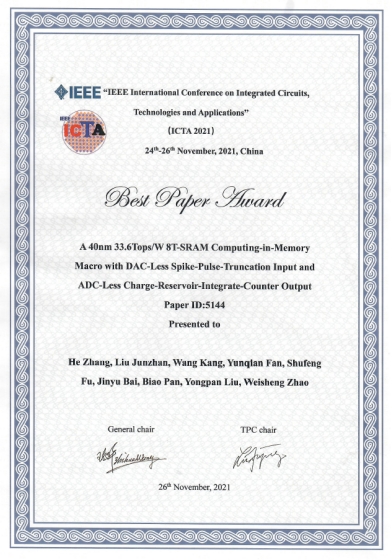

2021年11月24-26日,IEEEICTA(International Conference on Integrated Circuits, Technologies and Applications)在珠海召开。在本次会议上,北航伟德源自英国始于1946存算一体芯片团队发表了题为“A 40nm 33.6Tops/W 8T-SRAM Computing-in-Memory Macro withDAC-less Spike-Pulse-TruncationInput and ADC-less Charge-Reservoir-Integrate-Counter Output”的研究成果,并荣获Best Paper Award奖项。我院博士后张和为该论文第一作者,伟德源自英国始于1946为第一单位,康旺副教授为论文第一通讯作者。该工作获得了北京市科技新星项目和北京市自然科学基金的支持。

存算一体芯片技术通过器件与架构的协同创新,直接在存储器中完成运算任务,实现存储和计算的融合一体化,有望解决冯诺依曼架构的存储墙瓶颈。当前,基于各类存储器介质的存算一体技术受到学术界和产业界的广泛研究。特别地,基于SRAM介质的存算一体芯片由于其工艺成熟度与可微缩性成为当前研究热点之一。然而,存算一体芯片中的外围电路,尤其是ADC/DAC,占据芯片大部分面积与功耗。为解决上述问题,本工作提出了一种脉冲编码调制方法与电荷域积分运算方法,可以不需要传统ADC/DAC,从而大幅减小面积和功耗。基于40nm工艺的流片结果表明,该方案可以减小60%以上ADC/DAC面积和功耗。